有个函数代码被分割了,我修复后IDA有个switch跳转没有识别出来。手动改switch的时候报了个错误,麻烦各位大神帮看下可能是哪方面出的问题或者这个错误是什么引起的,网上没找到类似资料。信息如果提供的不全麻烦指出来我补上:

报错信息:

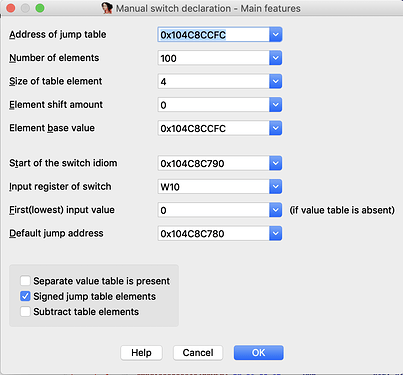

改跳转表:

原始Code:

__text:0000000104C8C780 loc_104C8C780 ; CODE XREF: __text:0000000104C84968↑j

__text:0000000104C8C780 ; __text:0000000104C84AF0↑j ...

__text:0000000104C8C780 E8 EF 41 B9 LDR W8, [SP,#0x1EC] ; Load from Memory

__text:0000000104C8C784 E9 F3 41 B9 LDR W9, [SP,#0x1F0] ; Load from Memory

__text:0000000104C8C788 EA 03 08 2A MOV W10, W8 ; Rd = Op2

__text:0000000104C8C78C EB 03 0A AA MOV X11, X10 ; Rd = Op2

__text:0000000104C8C790 0A 8D 01 71 SUBS W10, W8, #0x63 ; Rd = Op1 - Op2

__text:0000000104C8C794 EC 03 09 AA MOV X12, X9 ; Rd = Op2

__text:0000000104C8C798 ED 03 08 AA MOV X13, X8 ; Rd = Op2

__text:0000000104C8C79C E8 E3 01 B9 STR W8, [SP,#0x1E0] ; Store to Memory

__text:0000000104C8C7A0 E9 DF 01 B9 STR W9, [SP,#0x1DC] ; Store to Memory

__text:0000000104C8C7A4 EB EB 00 F9 STR X11, [SP,#0x1D0] ; Store to Memory

__text:0000000104C8C7A8 EA CF 01 B9 STR W10, [SP,#0x1CC] ; Store to Memory

__text:0000000104C8C7AC EC F3 01 B9 STR W12, [SP,#0x1F0] ; Store to Memory

__text:0000000104C8C7B0 ED EF 01 B9 STR W13, [SP,#0x1EC] ; Store to Memory

__text:0000000104C8C7B4 68 FE FF 54 B.HI loc_104C8C780 ; Branch

__text:0000000104C8C7B8 08 00 00 90 ADRP X8, #byte_104C8CCFC@PAGE ; Address of Page

__text:0000000104C8C7BC 08 F1 33 91 ADD X8, X8, #byte_104C8CCFC@PAGEOFF ; Rd = Op1 + Op2

__text:0000000104C8C7C0 E9 EB 40 F9 LDR X9, [SP,#0x1D0] ; Load from Memory

__text:0000000104C8C7C4 0A 79 A9 B8 LDRSW X10, [X8,X9,LSL#2] ; Load from Memory

__text:0000000104C8C7C8 3F E4 FF 17 B loc_104C858C4 ; Branch

__text:0000000104C858C4 loc_104C858C4 ; CODE XREF: __text:0000000104C8C7C8↓j

__text:0000000104C858C4 1F 20 03 D5 NOP ; No Operation

__text:0000000104C858C8 48 01 08 8B ADD X8, X10, X8 ; Rd = Op1 + Op2

__text:0000000104C858CC EB DF 41 B9 LDR W11, [SP,#0x1DC] ; Load from Memory

__text:0000000104C858D0 EC E3 41 B9 LDR W12, [SP,#0x1E0] ; Load from Memory

__text:0000000104C858D4 EC EF 01 B9 STR W12, [SP,#0x1EC] ; Store to Memory

__text:0000000104C858D8 76 15 00 14 B loc_104C8AEB0 ; Branch

__text:0000000104C8AEB0 loc_104C8AEB0 ; CODE XREF: __text:0000000104C858D8↑j

__text:0000000104C8AEB0 1F 20 03 D5 NOP ; No Operation

__text:0000000104C8AEB4 EB F3 01 B9 STR W11, [SP,#0x1F0] ; Store to Memory

__text:0000000104C8AEB8 00 01 1F D6 BR X8 ; Branch To Register